点击上方蓝字谈思实验室

获取更多汽车网络安全资讯

01

概览篇

芯片生产过程中引入的问题

1.制程缺陷-物理瑕疵

2.制程以外的缺陷

「一个非门的版图中常见的fail」

什么是DFT?为什么要做DFT?

1.Testing

2.DFT

3.测试阶段

测试结果的评价

1.Fault Coverage

体现了DFT的质量

SOC的DFT策略以及全芯片测试的内容

1.SOC的DFT策略

SOC ( System on Chip)是在同一块芯片中集成了CPU、各种存储器、总线系统、专用模块以及多种l/O接口的系统级超大规模集成电路。

由于SOC芯片的规模比较大、内部模块的类型以及来源多样,因此SOC芯片的DFT面临着诸多问题。

2.SOC涉及到的测试问题

3.SOC的全面测试

谁的风险高就先测谁,DC一般都是第一。

DC test-DC参数测试

基于SCAN的测试

BIST-内建自测试

BIST的种类与应用

LogicBIST技术的优缺点

Boundary Scan—JTAG

三种不同的协议,不同的功能,不同支持。

Boundary Scan 芯片与PAD之间连通性。FT

function pattern

ESD test

ETC.

DFT在整个IC设计中的位置

DFT与左边四个都会有不同程度的涉及。

大多数会把DFT放到Flow里面。

DFT的流程以及每步做的事情

1.A DFT reference flow

The sequence of each DFT steps can be changed

Test ltems—理论基础与工具实现

高亮的内容是DFT需要重点关注的。

2.Scan Based Test

还有基于latch,但是非主流

3.Fault model VS. Defect

4.Stuck-at Fault———用于低速测试

5.At-Speed Fault———用于在速测试

6.Transition Delay Fault Model

7.Path Delay model

8.D算法

9.How Scan Test works

这是一个pattern

10.Transition Launch Mode

11.Full scan & Partial scan

12.ATSPEED TEST & OCC

Scan chain synthesis flow——综合以后加入

Compression

减少测试时间

13.Multi-power DFT

功耗

FUNC下可能会多个电压阈

但是DFT下面一般都是单个

大芯片多个电路全电压说不定会烧测试几台:极少

ATPG-Automatic Test Pattern Generation

ATPG Focus

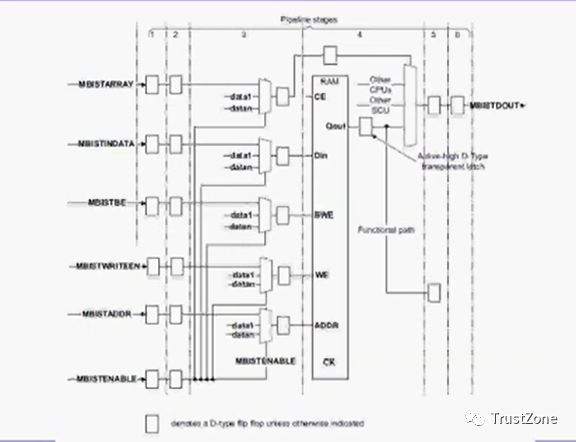

MBIST——综合之前或之后

14.Compressor for ROM

15.Deal with shadow logic

16.High Speed Core MBIST

17.LBIST

18.Boundary Scan

19.Boundary scan architecture

20.制程缺陷-物理瑕疵

21.TAP Ports Hookup Pin (After Synthesis)

22.IDDQ

23.IDDQ defect

24.Powerfault IDDQ

Points to be considered related to DFT

02

实战篇

前面都是理论,后续的深入,请各位感兴趣的自行去进一步的深入,我已经将完整的课程表单放在了这里。

Scan Chain的原理与实现

详细讲解基于Scan测试的各个细节,Scan Chain的实现。

Pattern压缩的原理与实现。

测试违反的初步分析与处理,测试覆盖率的预估

OCC的原理与实现

相关工具:DFT Compiler,DFTAdvisor,TestKompress

Scan Chain ATPG的原理与实现

Scan Chain违反的分析与处理

ATPG的实现流程

ATPG的低功耗考虑及动态IRDROP

分别讲述stuck-at、at-speed、 iddq等pattern的原理与产生

如何使测试覆盖率达到目标

相关工具:Tetramax,Fastscan,TestKompress

Memory BIST与Logic BIST的原理与实现

详细讲解Memory BIST的原理与实现

基于mbistarchitect的MBIST流程

基于Tessent Memory BIST的MBIST流程

shadow logic的scan考虑

share bus技术与实现

可修复技术的原理与实现

简要介绍Logic BIST原理与实现

boundary scan的原理与实现

详细讲解boundary scan的协议、原理

基于BSD Compiler的boundary scan实现

基于BSD Compiler的boundary scan pattern产生

测试模式下的timing以及flow考虑

timing constraint基础

各测试模式下timing的特点与注意事项

timing constraint的合并

formal check的DFT考虑

multi voltage设计的DFT考虑

测试pattern的仿真验延

仿真验证基础

工具使用,前仿、后仿

memorybist的仿真验证

scan pattern的仿真验证

boundary scan pattern的仿真验证

机台测试与问题诊断

ATE原理,load board准备。

CP、FT与burn-in测试等

问题处理与Diagnosis流程

DC测试、Shamoo测试、ESD测试与设计考虑

来源:TrustZone

精品活动推荐

更多文章

会员权益: (点击可进入)谈思实验室VIP会员

如有侵权请联系:admin#unsafe.sh